自我陈述

学了一点点 C++,Go 和 Rust,可以解决除了算法外的几乎所有代码问题。完全不会linux,会一点点LLVM/MLIR,WebAssembly,eBPF 和 Z3。AI

是业余有空会开发开发的小东西。如果你觉得我写的代码或者发的 paper 没有 novelty 或者垃圾的要死,绝对不是你的问题,欢迎邮件来喷!我的研究目标是利用 CXL 和 UCIe

技术在现代异构架构和通用处理器上加速数据访问和操作,以满足不同公司的工作负载。我相信硬件-软件协同设计的方法。硬件在不牺牲异构处理性能的前提下,通过对工作负载的深入了解,为常见的情况提供专门的加速能力,而软件则通过发送语义提示,自适应地利用硬件的优势,并在硬件加速无法实现时,退回到其他较慢的路径。我对寻求新知识和商业机会有极大的热情,并位于两个大都市——旧金山湾区和上海,我很自豪能学到更多的东西,使他人受益更多,赚得更多。

fn research_no_failure()->Result < Paper, Error > {

let output = if cfg!(target_os = "linux") {

Command::new("qemu-x86_64-system")

.args(["-smp 6", "-numa node,cpus=0-7,memdev=mem0,nodeid=0", "-object memory-backend-ram,id=mem0,size=8G","-numa node,cpus=8-15,memdev=mem1,nodeid=1", "-object memory-backend-ram,id=mem1,size=8G","-m 16G,slots=4,maxmem=32G", "-machine q35,cxl=on", "-M cxl-fmw.0.targets.0=cxl.1,cxl-fmw.0.size=4G",

"-device pxb-cxl,bus_nr=12,bus=pcie.0,id=cxl3.1", "-device cxl-rp,port=0,bus=cxl.1,id=root_port13,chassis=0,slot=2",

"-device cxl-type3,bus=root_port13,memdev=cxl-mem1,lsa=cxl-lsa1,id=cxl-mem0",

"-device cxl-type2,bus=root_port14,virtio-gpu-cxl,id=gpu0,gpudev=gpudev0"])

"-device cxl-type1,bus=root_port15,virtio-crypto-cxl,id=crypto0,cryptodev=cryptodev0"])

.output()

.expect("failed to execute process")

}

let paper = Paper::new(output);

loop{

asm!("clflush" :: "r" (&paper.iter()) : "rax", "rbx", "rcx", "rdx": "volatile" );

__atomic_thread_fence(__ATOMIC_SEQ_CST);

if (paper.is_valid()){

break;

}

}

Ok(paper)

}

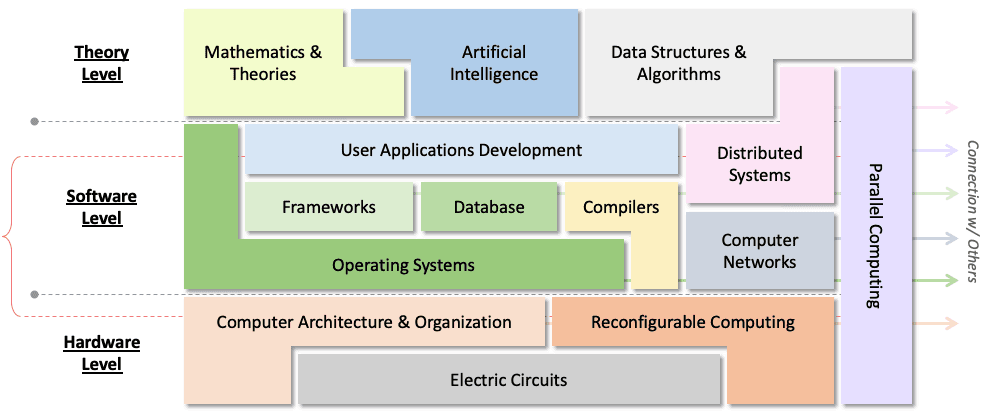

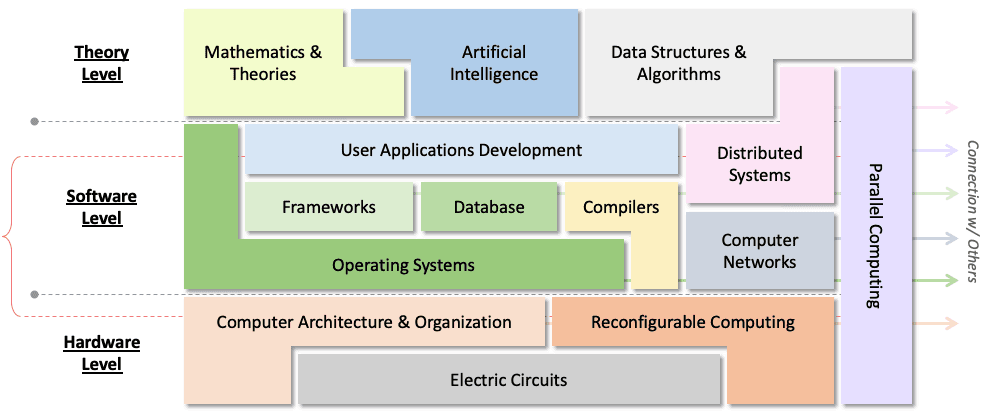

技能