文章目录[隐藏]

Previously in CS211

- Iron law of performance:

- time/program = insts/program * cycles/inst * time/cycle

- Classic 5-stage RISC pipeline

- Structural, data, and control hazards

- Structural hazards handled with interlock or more hardware

- Data hazards include RAW, WAR, WAW

- Handle data hazards with interlock, bypass, or speculation

- Control hazards (branches, interrupts) most difficult as change which is next instruction

- Branch prediction commonly used

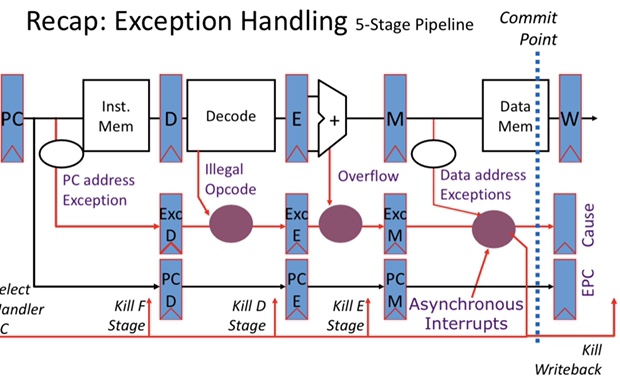

- Precise traps: stop cleanly on one instruction, all previous instructions completed, no following instructions have changed architectural state

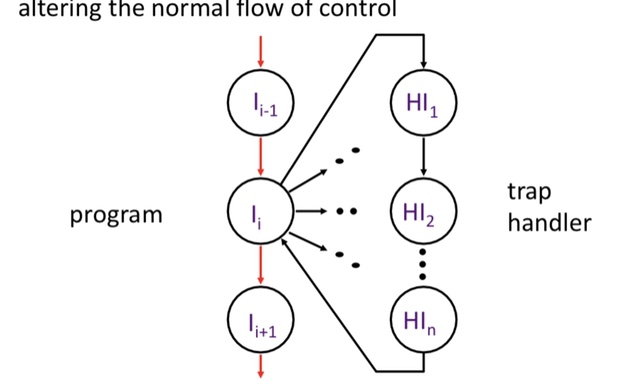

## Trap

An external or internal event that needs to be processed by another (system) program. The event is usually unexpected or rare from program’s point of view.

Handler

- Save \(EPC\) before enabling interrupts to allow nested interrupts

- need instruction to move \(EPC\) into GPR

- need a way to mask further interrupts.

- Needs to read a status register that indicates the cause of the trap.

- jump inst \(ERET\)

Synchronous Trap

- A synchronous trap is caused by an exception on a

- In general, the instruction cannot be completed and needs to be restarted after the exception has been handled

- requires undoing the effect of one or more partially executed instructions

- In the case of a system call trap, the instruction is considered to have been completed

- a special jump instruction involving a change to a privileged mode

Speculating on Exceptions • Prediction mechanism

- Exceptions are rare, so simply predicting no exceptions is very accurate!

- Check prediction mechanism

- Exceptions detected at end of instruction execution pipeline, special

hardware for various exception types • Recovery mechanism - Only write architectural state at commit point, so can throw away partially executed instructions after exception

- Launch exception handler after flushing pipeline

- Bypassing allows use of uncommitted instruction results by following instructions