Biography

I'm a third-year Computer Science System Ph.D. student @BaskinEng. I'm

honored to be advised by Andi Quinn, and hacking on

cutting-edge HW/SW co-design. The goal of my research is to accelerate data access and manipulation on

modern heterogeneous architecture and general-purpose processors for diverse workloads across companies

utilizing CXL and UCIe technology. I believe in a

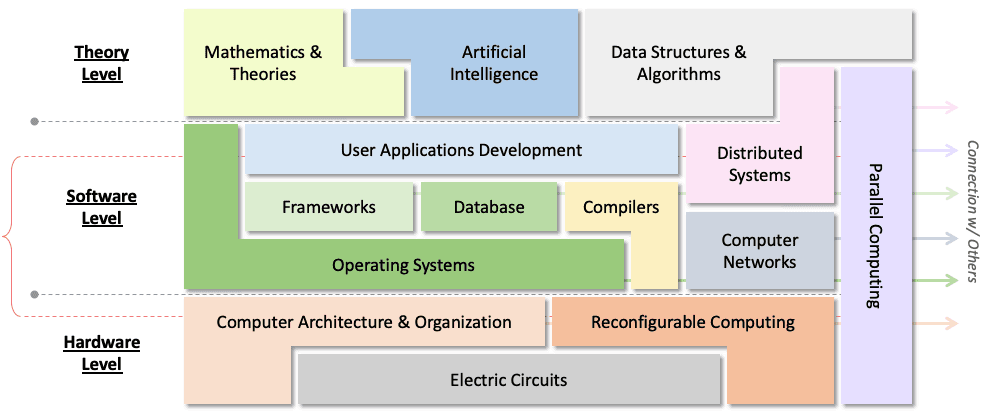

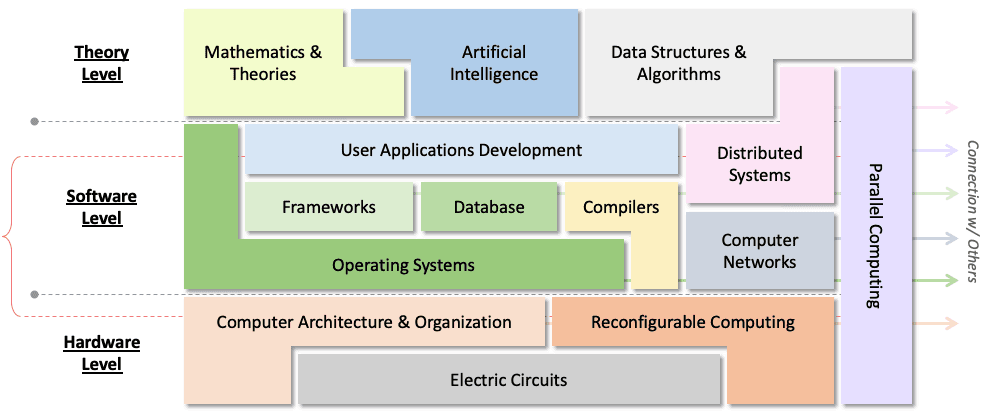

hardware-software

co-design methodology. The hardware provides specialized acceleration capabilities for common cases

without sacrificing heterogeneous processing performance with a better knowledge of workloads, while the

software adaptively takes advantage of the hardware by sending semantic hints, and falls back to

alternative, slower paths whenever hardware acceleration is not achievable. Assured with my great

passion for seeking new knowledge and commercial opportunity and situated in two metropolitans, the San

Fransisco Bay area, and Shanghai, I'm proud to learn more, benefit others more, and earn more.

Previously, I was an undergraduate @ShanghaiTech.

fn research_no_failure()->Result < Paper, Error > {

let output = if cfg!(target_os = "linux") {

Command::new("qemu-x86_64-system")

.args(["-smp 6", "-numa node,cpus=0-7,memdev=mem0,nodeid=0", "-object memory-backend-ram,id=mem0,size=8G","-numa node,cpus=8-15,memdev=mem1,nodeid=1", "-object memory-backend-ram,id=mem1,size=8G","-m 16G,slots=4,maxmem=32G", "-machine q35,cxl=on", "-M cxl-fmw.0.targets.0=cxl.1,cxl-fmw.0.size=4G",

"-device pxb-cxl,bus_nr=12,bus=pcie.0,id=cxl3.1", "-device cxl-rp,port=0,bus=cxl.1,id=root_port13,chassis=0,slot=2",

"-device cxl-type3,bus=root_port13,memdev=cxl-mem1,lsa=cxl-lsa1,id=cxl-mem0",

"-device cxl-type2,bus=root_port14,virtio-gpu-cxl,id=gpu0,gpudev=gpudev0"])

"-device cxl-type1,bus=root_port15,virtio-crypto-cxl,id=crypto0,cryptodev=cryptodev0"])

.output()

.expect("failed to execute process")

}

let paper = Paper::new(output);

loop{

asm!("clflush" :: "r" (&paper.iter()) : "rax", "rbx", "rcx", "rdx": "volatile" );

__atomic_thread_fence(__ATOMIC_SEQ_CST);

if (paper.is_valid()){

break;

}

}

Ok(paper)

}

Skills

Current Research

Research Assistant

August 2022 - Present

- Understanding the performance characteristics of CXL.mem systems. Data-driven far

memory allocation, prefetching, and

replacement policies. Emulating memory disaggregation for data center applications

- Make Hardware Software Co-design for on CXL.cache data movement

- Make universal migration based on WebAssembly and PTX

- Make cross kernel-userspace eBPF observation for distributed system